A1321, A1322, and A1323

# Ratiometric Linear Hall Effect Sensor ICs for High-Temperature Operation

| <b>Discontinued Proc</b>                                                                                                                                                                                                                                                                           | luct                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| This device is no longer in production. The device purchased for new design applications. Samples are                                                                                                                                                                                              |                             |

| Date of status change: October 31, 2011<br>• for the A1321EUA-T and the A1321LUA-T use th<br>• for the A1321ELHLT-T and the A1321LLHLT-T<br>• for the A1322LUA-T use the <u>A1325LUA-T</u><br>• for the A1322LLHLT-T use the <u>A1325LLHLX-T</u><br>• for the A1323EUA-T and the A1323LUA-T use th | use the <u>A1324LLHLX-T</u> |

| • for the A1323LLHLT-T use the <u>A1326LLHLX-T</u>                                                                                                                                                                                                                                                 |                             |

| NOTE: For detailed information on purchasing opt<br>local Allegro field applications engineer or sales rep                                                                                                                                                                                         | -                           |

Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

# A1321, A1322, and A1323

#### Ratiometric Linear Hall Effect Sensor ICs for High-Temperature Operation

#### **Features and Benefits**

- Temperature-stable quiescent output voltage

- Precise recoverability after temperature cycling

- Output voltage proportional to magnetic flux density

- Ratiometric rail-to-rail output

- Improved sensitivity

- 4.5 to 5.5 V operation

- Immunity to mechanical stress

- Solid-state reliability

- Robust EMC protection

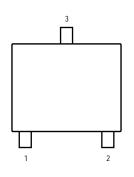

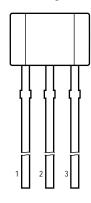

# Packages: 3 pin SOT23W (suffix LH), and 3 pin SIP (suffix UA)

Not to scale

#### Description

The A132X family of linear Hall-effect sensor ICs are optimized, sensitive, and temperature-stable. These ratiometric Hall-effect sensor ICs provide a voltage output that is proportional to the applied magnetic field. The A132X family has a quiescent output voltage that is 50% of the supply voltage and output sensitivity options of 2.5 mV/G, 3.125 mV/G, and 5m V/G. The features of this family of devices are ideal for use in the harsh environments found in automotive and industrial linear and rotary position sensing systems.

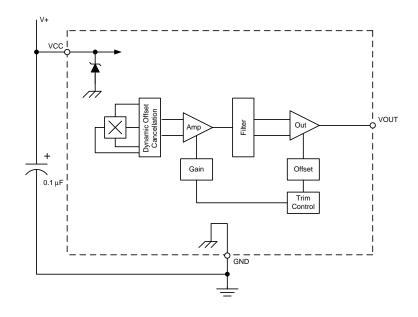

Each device has a BiCMOS monolithic circuit which integrates a Hall element, improved temperature-compensating circuitry to reduce the intrinsic sensitivity drift of the Hall element, a small-signal high-gain amplifier, and a rail-to-rail lowimpedance output stage.

A proprietary dynamic offset cancellation technique, with an internal high-frequency clock, reduces the residual offset voltage normally caused by device overmolding, temperature dependencies, and thermal stress. The high frequency clock allows for a greater sampling rate, which results in higher accuracy and faster signal processing capability. This technique produces devices that have an extremely stable quiescent output voltage, are immune to mechanical stress, and have precise

Continued on the next page...

#### **Functional Block Diagram**

#### **Description (continued)**

recoverability after temperature cycling. Having the Hall element and an amplifier on a single chip minimizes many problems normally associated with low-level analog signals.

Output precision is obtained by internal gain and offset trim adjustments made at end-of-line during the manufacturing process.

The A132X family is provided in a 3-pin single in-line package (UA) and a 3-pin surface mount package (LH). Each package is available in a lead (Pb) free version (suffix, -T), with a 100% matte tin plated leadframe.

#### **Selection Guide**

| Part Number               | Packing <sup>1</sup>         | Mounting         | Ambient, T <sub>A</sub><br>(ºC) | Sensitivity,<br>Typ. (mV/G) |  |

|---------------------------|------------------------------|------------------|---------------------------------|-----------------------------|--|

| A1321ELHLT-T <sup>2</sup> | 7-in. reel, 3000 pieces/reel | Surface Mount    | 40 to 95                        |                             |  |

| A1321EUA-T3               | Bulk, 500 pieces/bag         | SIP through hole |                                 | F 000                       |  |

| A1321LLHLT-T <sup>2</sup> | 7-in. reel, 3000 pieces/reel | Surface Mount    | 40 to 150                       | 5.000                       |  |

| A1321LUA-T3               | Bulk, 500 pieces/bag         | SIP through hole | -40 10 150                      |                             |  |

| A1322LLHLT-T <sup>2</sup> | 7-in. reel, 3000 pieces/reel | Surface Mount    | 10 to 150                       | 3.125                       |  |

| A1322LUA-T3               | Bulk, 500 pieces/bag         | SIP through hole | -40 10 150                      |                             |  |

| A1323EUA-T3               | Bulk, 500 pieces/bag         | SIP through hole | -40 to 85                       |                             |  |

| A1323LLHLT-T2             | 7-in. reel, 3000 pieces/reel | Surface Mount    | 40 to 150                       | 2.500                       |  |

| A1323LUA-T3               | Bulk, 500 pieces/bag         | SIP through hole | -40 (0 150                      |                             |  |

<sup>1</sup>Contact Allegro for additional packing options.

<sup>2</sup>This variant is in production, however, it has been deemed Pre-End of Life. The product is approaching end of life. Within a minimum of 6 months, the device will enter its final, Last Time Buy, order phase. Status change: January 31, 2011. Suggested replacements: for the A1321ELHLT-T and the A1321LLHLT-T use the A1324LLHLX-T, for the A1324LLHLT-T use the A1325LLHLX-T, and for the A1323LLHLT-T use the A1326LLHLX-T. <sup>3</sup>Variant is in production but has been determined to be NOT FOR NEW DESIGN. This classification indicates that sale of the variant is currently restricted to existing customer applications. The variant should not be purchased for new design applications because obsolescence in the near future is probable. Samples are no longer available. Status change: January 31, 2011.

#### **Absolute Maximum Ratings**

| Characteristic                | Symbol               | Notes                                                                                                                                                            | Rating     | Units |

|-------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| Supply Voltage                | V <sub>CC</sub>      | <sup>*</sup> Additional current draw may be observed at voltages above the minimum supply Zener clamp voltage, $V_{Z(min)}$ , due to the Zener diode turning on. | 8          | V     |

| Output Voltage                | V <sub>OUT</sub>     |                                                                                                                                                                  | 8          | V     |

| Reverse Supply Voltage        | V <sub>RCC</sub>     |                                                                                                                                                                  | -0.1       | V     |

| Reverse Output Voltage        | V <sub>ROUT</sub>    |                                                                                                                                                                  | -0.1       | V     |

| Output Sink Current           | I <sub>OUT</sub>     |                                                                                                                                                                  | 10         | mA    |

| Operating Ambient Temperature | T <sub>A</sub>       | Range L                                                                                                                                                          | -40 to 150 | °C    |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                                                                                                                                                                  | 165        | °C    |

| Storage Temperature           | T <sub>stg</sub>     |                                                                                                                                                                  | -65 to 170 | °C    |

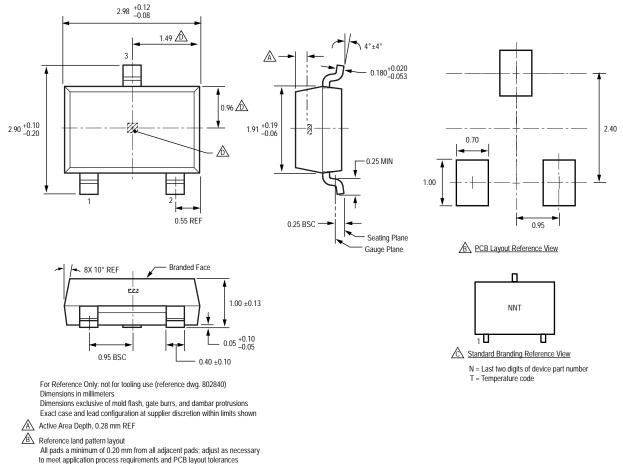

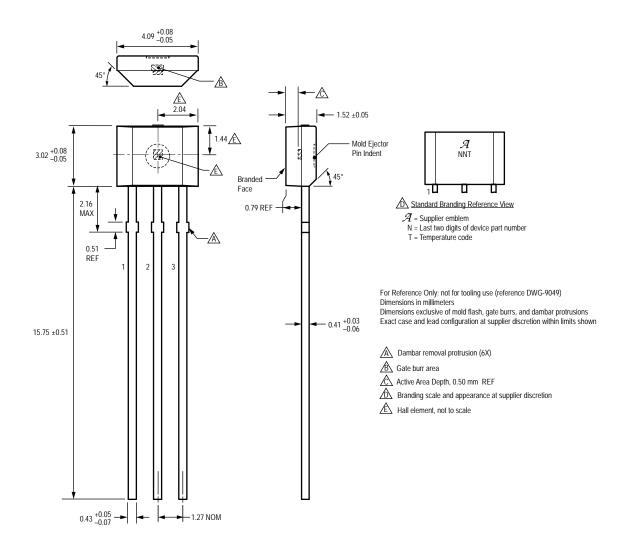

**Pin-out Drawings**

Package LH

Package UA

#### Terminal List

| Symbol | Nun        | nber       | Description                   |

|--------|------------|------------|-------------------------------|

| Symbol | Package LH | Package UA | Description                   |

| VCC    | 1          | 1          | Connects power supply to chip |

| VOUT   | 2          | 3          | Output from circuit           |

| GND    | 3          | 2          | Ground                        |

| Characteristic                                                            | Symbol               | Test Conditions                                       | Min.  | Typ. <sup>2</sup> | Max.  | Units |  |

|---------------------------------------------------------------------------|----------------------|-------------------------------------------------------|-------|-------------------|-------|-------|--|

| Electrical Characteristics; V <sub>CC</sub> = 5 V, unless otherwise noted |                      |                                                       |       |                   |       |       |  |

| Supply Voltage                                                            | V <sub>cc(op)</sub>  | Operating; Tj < 165°C                                 | 4.5   | 5.0               | 5.5   | V     |  |

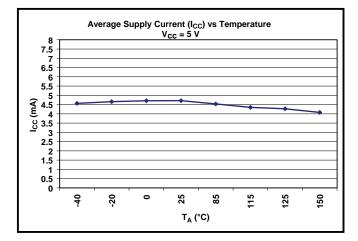

| Supply Current                                                            | I <sub>cc</sub>      | $B = 0, I_{out} = 0$                                  | -     | 5.6               | 8     | mA    |  |

| Quiescent Voltage                                                         | V <sub>out(q)</sub>  | B = 0, T <sub>A</sub> = 25°C, I <sub>out</sub> = 1 mA | 2.425 | 2.5               | 2.575 | V     |  |

| Output Voltage <sup>3</sup>                                               | V <sub>out(H)</sub>  | $B = +X$ , $I_{out} = -1 mA$                          | -     | 4.7               | -     | V     |  |

| Culput Voltage                                                            | V <sub>out(L)</sub>  | $B = -X$ , $I_{out} = 1 mA$                           | -     | 0.2               | -     | V     |  |

| Output Source Current Limit <sup>3</sup>                                  | I <sub>out(LM)</sub> | $B = -X, V_{out} \rightarrow 0$                       | -1.0  | -1.5              | -     | mA    |  |

| Supply Zener Clamp Voltage                                                | Vz                   | $I_{cc} = 11 \text{ mA} = I_{cc(max)} + 3$            | 6     | 8.3               | -     | V     |  |

| Output Bandwidth                                                          | BW                   |                                                       | -     | 30                | -     | kHz   |  |

| Clock Frequency                                                           | f <sub>C</sub>       |                                                       | -     | 150               | -     | kHz   |  |

| Output Characteristics; over $V_{CC}$                                     | range, unless o      | otherwise noted                                       |       |                   |       |       |  |

|                                                                           |                      | A1321; C <sub>bypass</sub> = 0.1 µF, no load          | -     | -                 | 40    | mV    |  |

| Noise, Peak-to-Peak <sup>4</sup>                                          | V <sub>N</sub>       | A1322; C <sub>bypass</sub> = 0.1 µF, no load          | -     | -                 | 25    | mV    |  |

|                                                                           |                      | A1323; C <sub>bypass</sub> = 0.1 µF, no load          | -     | -                 | 20    | mV    |  |

| Output Resistance                                                         | R <sub>out</sub>     | I <sub>out</sub> ≤±1 mA                               | -     | 1.5               | 3     | Ω     |  |

| Output Load Resistance                                                    | RL                   | $I_{out} \le \pm 1$ mA, VOUT to GND                   | 4.7   | -                 | -     | kΩ    |  |

| Output Load Capacitance                                                   | CL                   | VOUT to GND                                           | -     | -                 | 10    | nF    |  |

#### **DEVICE CHARACTERISTICS**<sup>1</sup> over operating temperature (T<sub>A</sub>) range, unless otherwise noted

<sup>1</sup> Negative current is defined as conventional current coming out of (sourced from) the specified device terminal.

<sup>2</sup> Typical data is at  $T_A = 25^{\circ}$ C. They are for initial design estimations only, and assume optimum manufacturing and application conditions. Performance may vary for individual units, within the specified maximum and minimum limits.

<sup>3</sup> In these tests, the vector **X** is intended to represent positive and negative fields sufficient to swing the output driver between fully OFF and saturated (ON), respectively. It is NOT intended to indicate a range of linear operation.

<sup>4</sup> Noise specification includes both digital and analog noise.

| Characteristics                                             | Symbol                     | Test Condition                                                | Min   | Typ <sup>3</sup> | Max   | Units <sup>4</sup> |

|-------------------------------------------------------------|----------------------------|---------------------------------------------------------------|-------|------------------|-------|--------------------|

|                                                             |                            | A1321; T <sub>A</sub> = 25°C                                  | 4.750 | 5.000            | 5.250 | mV/G               |

| Sensitivity <sup>5</sup>                                    | Sens                       | A1322; T <sub>A</sub> = 25°C                                  | 2.969 | 3.125            | 3.281 | mV/G               |

| -                                                           |                            | A1323; T <sub>A</sub> = 25°C                                  | 2.375 | 2.500            | 2.625 | mV/G               |

| Delta V <sub>out(q)</sub> as a func-<br>tion of temperature | V <sub>out(q)(ΔT)</sub>    | Defined in terms of magnetic flux density, B                  | _     | _                | ±10   | G                  |

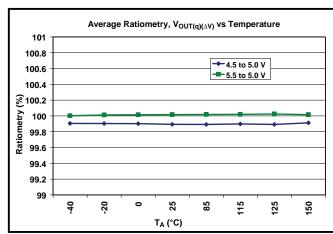

| Ratiometry, V <sub>out(q)</sub>                             | $V_{out(q)(\Delta V)}$     |                                                               | _     | _                | ±1.5  | %                  |

| Ratiometry, Sens                                            | $\Delta Sens_{(\Delta V)}$ |                                                               | _     | _                | ±1.5  | %                  |

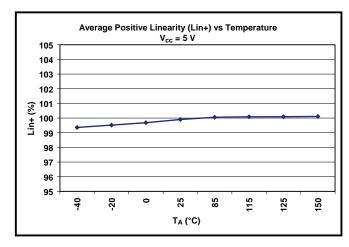

| Positive Linearity                                          | Lin+                       |                                                               | _     | _                | ±1.5  | %                  |

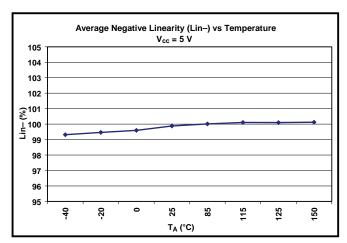

| Negative Linearity                                          | Lin–                       |                                                               | _     | _                | ±1.5  | %                  |

| Symmetry                                                    | Sym                        |                                                               | _     | -                | ±1.5  | %                  |

| UA Package                                                  |                            |                                                               |       |                  |       |                    |

| Delta Sens at T <sub>A</sub> = max <sup>5</sup>             | $\Delta Sens_{(TAmax)}$    | From hot to room temperature                                  | -2.5  | -                | 7.5   | %                  |

| Delta Sens at T <sub>A</sub> = min <sup>5</sup>             | ΔSens <sub>(TAmin)</sub>   | From cold to room temperature                                 | -6    | -                | 4     | %                  |

| Sensitivity Drift <sup>6</sup>                              | Sens <sub>Drift</sub>      | $T_A = 25^{\circ}C$ ; after temperature cycling and over time | -     | ±2               | -     | %                  |

| LH Package                                                  |                            |                                                               |       |                  |       |                    |

| Delta Sens at T <sub>A</sub> = max <sup>5</sup>             | $\Delta Sens_{(TAmax)}$    | From hot to room temperature                                  | -5    | _                | 5     | %                  |

| Delta Sens at T <sub>A</sub> = min <sup>5</sup>             | ΔSens <sub>(TAmin)</sub>   | From cold to room temperature                                 | -3.5  | _                | 8.5   | %                  |

| Sensitivity Drift <sup>6</sup>                              | Sens <sub>Drift</sub>      | $T_A = 25^{\circ}C$ ; after temperature cycling and over time | _     | ±2               | _     | %                  |

<sup>1</sup> Additional information on characteristics is provided in the section Characteristics Definitions, on the next page.

<sup>2</sup> Negative current is defined as conventional current coming out of (sourced from) the specified device terminal.

<sup>3</sup> Typical data is at  $T_A = 25^{\circ}$ C, except for  $\Delta$ Sens, and at *x.x* Sens. Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions. Performance may vary for individual units, within the specified maximum and minimum limits. In addition, the typical values vary with gain.

<sup>4</sup> 10 G = 1 millitesla.

<sup>5</sup> After 150°C pre-bake and factory programming.

<sup>6</sup> Sensitivity drift is the amount of recovery with time.

#### A1321, A1322, and A1323

### Ratiometric Linear Hall Effect Sensor ICs for High-Temperature Operation

#### **Characteristic Definitions**

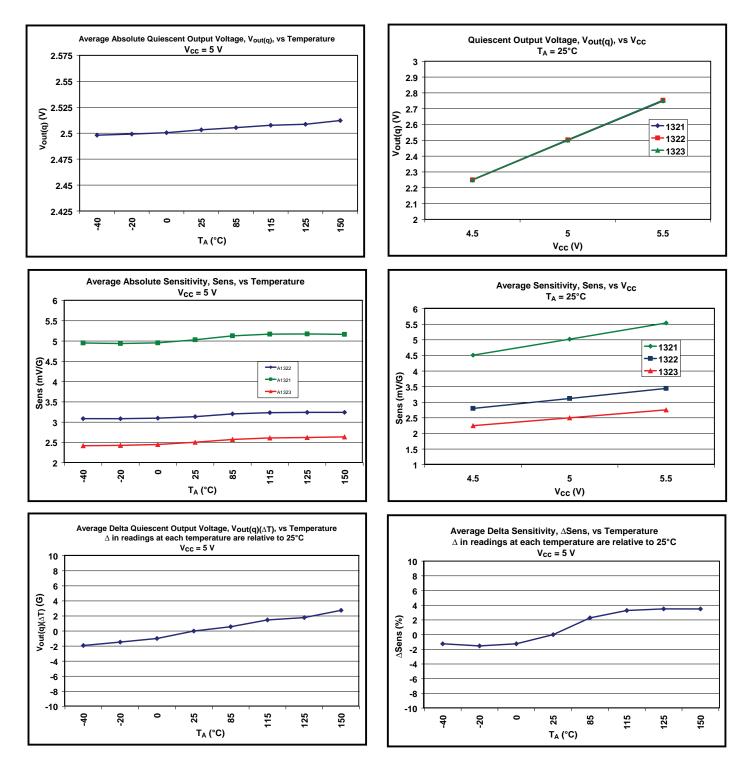

**Quiescent Voltage Output.** In the quiescent state (no magnetic field), the output equals one half of the supply voltage over the operating voltage range and the operating temperature range. Due to internal component tolerances and thermal considerations, there is a tolerance on the quiescent voltage output both as a function of supply voltage and as a function of ambient temperature. For purposes of specification, the quiescent voltage output as a function of temperature is defined in terms of magnetic flux density, B, as:

$$\Delta V_{\text{out}(q)(\Delta T)} = \frac{V_{\text{out}(q)(T_A)} - V_{\text{out}(q)(25^\circ\text{C})}}{\text{Sens}_{(25^\circ\text{C})}}$$

(1)

This calculation yields the device's equivalent accuracy, over the operating temperature range, in gauss (G).

**Sensitivity.** The presence of a south-pole magnetic field perpendicular to the package face (the branded surface) increases the output voltage from its quiescent value toward the supply voltage rail by an amount proportional to the magnetic field applied. Conversely, the application of a north pole will decrease the output voltage from its quiescent value. This proportionality is specified as the sensitivity of the device and is defined as:

Sens =

$$\frac{V_{\text{out}(-B)} - V_{\text{out}(+B)}}{2B}$$

(2)

The stability of sensitivity as a function of temperature is defined as:

$$\Delta \text{Sens}_{(\Delta T)} = \frac{\text{Sens}_{(T_A)} - \text{Sens}_{(25^\circ\text{C})}}{\text{Sens}_{(25^\circ\text{C})}} \times 100\%$$

(3)

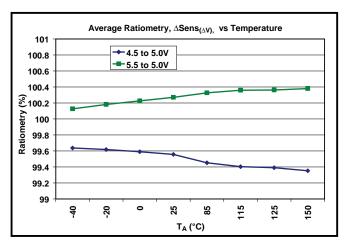

**Ratiometric.** The A132X family features a ratiometric output. The quiescent voltage output and sensitivity are proportional to the supply voltage (ratiometric).

The percent ratiometric change in the quiescent voltage output is defined as:

$$\Delta V_{\text{out}(q)(\Delta V)} = \frac{V_{\text{out}(q)(V_{\text{CC}})} / V_{\text{out}(q)(5V)}}{V_{\text{CC}} / 5 V} \times 100\%$$

(4)

and the percent ratiometric change in sensitivity is defined as:

$$\Delta \text{Sens}_{(\Delta \text{V})} = \frac{\text{Sens}_{(\text{V}_{\text{CC}})}/\text{Sens}_{(5\text{V})}}{\text{V}_{\text{CC}}/5 \text{ V}} \times 100\%$$

(5)

**Linearity and Symmetry.** The on-chip output stage is designed to provide a linear output with a supply voltage of 5 V. Although application of very high magnetic fields will not damage these devices, it will force the output into a non-linear region. Linearity in percent is measured and defined as:

$$Lin+ = \frac{V_{out(+B)} - V_{out(q)}}{2(V_{out(+B/2)} - V_{out(q)})} \times 100\%$$

(6)

$$Lin = \frac{V_{out(-B)} - V_{out(q)}}{2(V_{out(-B/2)} - V_{out(q)})} \times 100\%$$

(7)

and output symmetry as:

$$Sym = \frac{V_{out(+B)} - V_{out(q)}}{V_{out(q)} - V_{out(-B)}} \times 100\%$$

(8)

Typical Characteristics (30 pieces, 3 fabrication lots)

#### A1321, A1322, and A1323

# Ratiometric Linear Hall Effect Sensor ICs for High-Temperature Operation

Typical Characteristics, continued (30 pieces, 3 fabrication lots)

#### A1321, A1322, and A1323

# Ratiometric Linear Hall Effect Sensor ICs for High-Temperature Operation

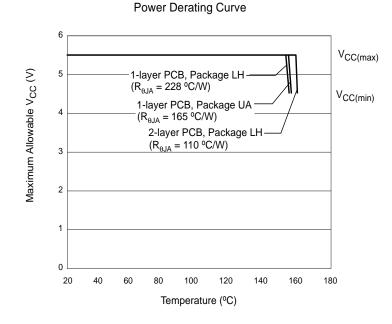

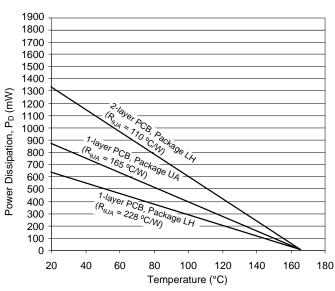

#### THERMAL CHARACTERISTICS may require derating at maximum conditions, see application information

| Characteristic             | Symbol           | Test Conditions*                                                                                       |     | Units |

|----------------------------|------------------|--------------------------------------------------------------------------------------------------------|-----|-------|

| Package Thermal Resistance |                  | Package LH, 1-layer PCB with copper limited to solder pads                                             | 228 | °C/W  |

|                            | κ <sub>θJA</sub> | Package LH, 2-layer PCB with 0.463 in. <sup>2</sup> of copper area each side connected by thermal vias | 110 | °C/W  |

|                            |                  | Package UA, 1-layer PCB with copper limited to solder pads                                             | 165 | °C/W  |

\*Additional thermal information available on Allegro website.

#### Power Derating

The device must be operated below the maximum junction temperature of the device,  $T_{J(max)}$ . Under certain combinations of peak conditions, reliable operation may require derating supplied power or improving the heat dissipation properties of the application. This section presents a procedure for correlating factors affecting operating  $T_J$ . (Thermal data is also available on the Allegro MicroSystems Web site.)

The Package Thermal Resistance,  $R_{\theta JA}$ , is a figure of merit summarizing the ability of the application and the device to dissipate heat from the junction (die), through all paths to the ambient air. Its primary component is the Effective Thermal Conductivity, K, of the printed circuit board, including adjacent devices and traces. Radiation from the die through the device case,  $R_{\theta JC}$ , is relatively small component of  $R_{\theta JA}$ . Ambient air temperature,  $T_A$ , and air motion are significant external factors, damped by overmolding.

The effect of varying power levels (Power Dissipation,  $P_D$ ), can be estimated. The following formulas represent the fundamental relationships used to estimate  $T_J$ , at  $P_D$ .

$$P_{D} = V_{IN} \times I_{IN} \qquad (1)$$

$$\Delta T = P_{D} \times R_{\theta JA} (2)$$

$$T_{I} = T_{A} + \Delta T \qquad (3)$$

For example, given common conditions such as:  $T_A = 25^{\circ}$ C,  $V_{CC} = 12$  V,  $I_{CC} = 4$  mA, and  $R_{\theta JA} = 140^{\circ}$ C/W, then:

$$\begin{split} P_D &= V_{CC} \times I_{CC} = 12 \text{ V} \times 4 \text{ mA} = 48 \text{ mW} \\ \Delta T &= P_D \times R_{0JA} = 48 \text{ mW} \times 140 \text{ °C/W} = 7 \text{ °C} \\ T_J &= T_A + \Delta T = 25 \text{ °C} + 7 \text{ °C} = 32 \text{ °C} \end{split}$$

A worst-case estimate,  $P_{D(max)}$ , represents the maximum allowable power level ( $V_{CC(max)}$ ,  $I_{CC(max)}$ ), without exceeding  $T_{J(max)}$ , at a selected  $R_{\theta JA}$  and  $T_A$ . *Example*: Reliability for  $V_{CC}$  at  $T_A=150^{\circ}$ C, package UA, using minimum-K PCB.

Observe the worst-case ratings for the device, specifically:  $R_{\theta JA}=165^{\circ}C/W$ ,  $T_{J(max)}=165^{\circ}C$ ,  $V_{CC(max)}=5.5$  V, and  $I_{CC(max)}=8$  mA.

Calculate the maximum allowable power level,  $P_{D(max)}$ . First, invert equation 3:

$$\Delta T_{max} = T_{J(max)} - T_A = 165 \,^{\circ}\text{C} - 150 \,^{\circ}\text{C} = 15 \,^{\circ}\text{C}$$

This provides the allowable increase to  $T_J$  resulting from internal power dissipation. Then, invert equation 2:

$$P_{D(max)} = \Delta T_{max} \div R_{\theta JA} = 15^{\circ}C \div 165^{\circ}C/W = 91 \text{ mW}$$

Finally, invert equation 1 with respect to voltage:

$$V_{CC(est)} = P_{D(max)} \div I_{CC(max)} = 91 \text{ mW} \div 8 \text{ mA} = 11.4 \text{ V}$$

The result indicates that, at  $T_A$ , the application and device can dissipate adequate amounts of heat at voltages  $\leq V_{CC(est)}$ .

Compare  $V_{CC(est)}$  to  $V_{CC(max)}$ . If  $V_{CC(est)} \leq V_{CC(max)}$ , then reliable operation between  $V_{CC(est)}$  and  $V_{CC(max)}$  requires enhanced  $R_{\theta JA}$ . If  $V_{CC(est)} \geq V_{CC(max)}$ , then operation between  $V_{CC(est)}$  and  $V_{CC(max)}$  is reliable under these conditions.

Package LH, 3-Pin (SOT-23W)

- Branding scale and appearance at supplier discretion

- Hall element, not to scale

Package UA, 3-Pin SIP

Copyright ©2004-2010, Allegro MicroSystems, Inc.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website: www.allegromicro.com